Gestion du bus de données :

Les transactions sur les données nécessitent de n’être effectuées qu’une seule fois, et nous avons vu qu’il était possible de recevoir deux cycles MCY dans un cycle TRS_ZMREQ le second pouvant être incomplet. Afin d’être certain que l’accès mémoire sera effectué sur le premier cycle, seul à être garanti d’être complet, il convient de créer un nouveau signal. Celui-ci sera créé sur le CPLD ADRESSE qui dispose des signaux nécessaires puis acheminé vers le CPLD DONNEES sur une ligne dédiée.

La signalisation du sens de transfert lecture ou écriture est également importante.

CPLD ADRESSES

PIN = RDWR ; /* SIGNALISATION D’UNE LECTURE */

PIN = MEMREQ ; /* SIGNALISATION DU PREMIER CRENEAU MCY6-7 PENDANT TRS_ZMREQ */

PIN = MEM_RW ;

PIN = MEM_OE

NODE = MREQ ; /* CONDITION D’ACCES */

NODE MEMACK : /* MEMOIRE INTERMEDIAIRE */

RDWR = RD ; /* ON TRANSMET LE SIGNAL RD VERS LE SECOND CPLD */

MREQ = TRS-A15 & !TRS_ZMREQ ;

MEMACK.d = MREQ ;

MEMACK.ck = MCY2 & !MEMACK ; /* DECLENCHEMENT A MCY4 (AVANT MCY6-7) */

MEMACK.ar = TRS_ZMREQ ; /* REVIENT A ZERO A LA FIN DE LA TRANSACTION */

MEMREQ.d = MREQ ; /* MEMORISATION DU PREMIER CRENEAU */

MEMREQ.ck = MEMACK ; /* LORS DE LA VALIDATION DE MEMACK QUI N’ARRIVE QU’UNE SEULE FOIS */

MEMREQ.ar = !MCY2 ; /* ARRET APRES MCY7 */

MEM_OE.d = !(MREQ & RDWR) ; /* VALIDATION EN SORTIE SUR UNE LECTURE */

MEM_OE.ck = CLK ;

MEM_RW.d = !(MEMREQ & MCY1 & !MCY0) ; /* LECTURE PAR DEFAUT, ECRITURE POSSIBLE UNIQUEMENT SUR LE CYCLE MCY6-7 */

MEM_RW.ck = CLK ;

Sur le Bus de données, Les données sont mémorisées pour être écrite vers la mémoire.

CPLD DONNEES

PIN = MEMREQ ; /* SIGNAL CREE PAR LE CPLD ADRESSE */

PIN = RDWR /* SENS DU TRANSFERT */

MEM_D0.d = TRS_D0 & MCY2 & MCY1 ; /* LA LECTURE S’EFFECTUE DANS LE CRENEAU MCY6-7 */

…

MEM_Dx.d = TRS_Dx & MCY2 & MCY1 ;

MEM_D0.ck = CLK ;

…

MEM_Dx.ck = CLK ;

MEM_D0.oe = MEMREQ & !RDWR & MCY2 & MCY1 ; /* LES DONNES SONT AUTORISEES A SORTIR SUR LE BUS EN CAS DE LECTURE */

…

MEM_Dx.oe = MEMREQ & !RDWR & MCY2 & MCY1 ;

Et à destination du bus d’extension :

CPLD DONNEES

TRS_D0.d = MEM_D0 & RDWR ; /* ON LIT LA MEMOIRE EN DE TRANSFERT EN LECTURE */

…

TRS_Dx.d = MEM_Dx & RDWR ;

TRS_D0.ck = CLK ;

…

TRS_Dx.ck = CLK ;

TRS_D0.oe = RDWR & MREQ; /* ON AUTORISE LA SORTIE SUR LE BUS DU TRS-80 UNIQUEMENT PENDANT LA REQUETE */

…

TRS_Dx.oe = RDWR & MREQ;

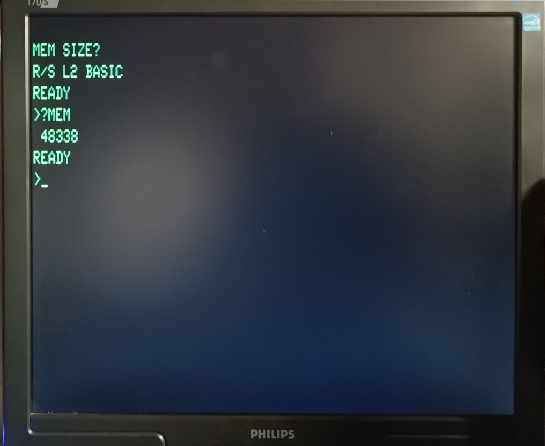

Afin de vérifier le bon fonctionnement il suffit de démarrer le TRS-80 avec sa carte vidéo et de regarder le volume de mémoire disponible. Il est passé de 15570 à 48338 octets. En effet pour dimensionner son espace mémoire, le TRS-80 lors de son initialisation écris et relit de manière continue dans la RAM jusqu’à ce qu’il trouve une erreur. Il y a erreur lorsqu'il tente d'accéder à un espace sans mémoire ou encore lorsqu'il repasse à $0000 adresse de la ROM non inscriptible, comme c'est le cas ici.

Dans les faits 814 octets de la RAM sont réservés par le système pour sa gestion interne, il reste donc 15570 octets pour une version 16ko et 48338 pour une extension de 32ko (utilisée ici pour nos deux fenêtres de 16ko).

Victoire, à ce stade, c’est bien ce que nous montre le TRS-80.