Premiers échanges en Interface avec le bus d’extension du TRS-80, le bus d'adresse

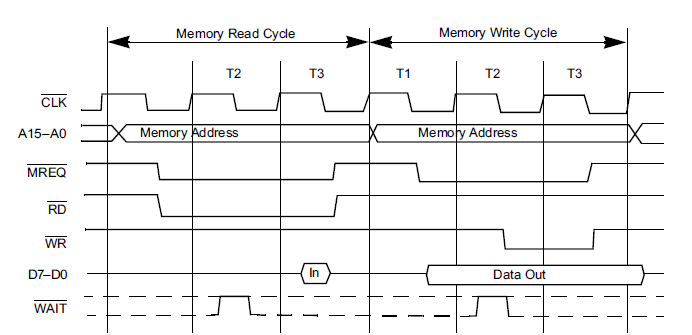

La lecture mémoire issue du TRS-80 utilise des signaux adaptés du Z80 qui est son processeur. Nous avons vu rapidement plus tôt comment ce passait une lecture mémoire voici maintenant l’ensemble des cycles d’accès à une mémoire ou un périphérique externe.

On remarque que le signal MREQ permet de bien encadrer les échanges de données. D’une durée de deux cycles d’horloge CPU soit environ 1,13µs (ici CLK est l’horloge du TRS-80 d'une valeur de 1,77MHz). Dans le même temps deux cycles mémoire valent donc 1,07µs (16 cycles de 66nS), nous pouvons donc garantir qu’il est possible d’anticiper la mise à disposition des données avant le cycle réservé à l’action de lecture/écriture vers la mémoire (MCY6-7).

Le bus d’adresse comme celui des don

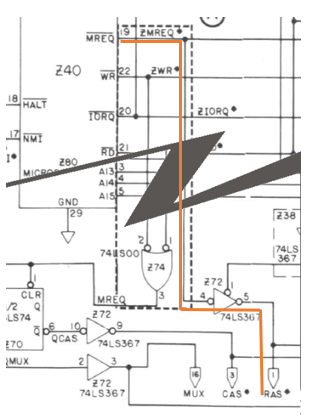

Cependant ne semble pas disponible sur le BUS d’extension pour la gestion des opérations de lecture et d’écriture sur la mémoire

On remarque, en revanche, sur le schéma du TRS-80 que ce dernier utilise néanmoins ce signal afin d’élaborer les signaux de gestion l’accès à la mémoire dynamique dont le bus d’adresse est multiplexé. Ce signal qui est en fait le même est renommé utilisé pour la sélection des colonnes.

Il est bien présent sur le BUS d’extension, nous l’appellerons TRS_ZMREQ.

nées est stable durant ce signal et la lecture ou l’écriture est terminé lorsqu’il n’est plus actif.

Cependant MREQ ne semble pas disponible sur le BUS d’extension du TRS-80 pour assurer la gestion des opérations de lecture et d’écriture sur la mémoire

On remarque en revanche, sur un schéma électrique du TRS-80 que ce dernier utilise néanmoins ce signal afin d’élaborer les signaux de gestion l’accès à la mémoire dynamique dont le bus d’adresse est multiplexé. Ce signal qui est en fait le même est renommé RAS et est utilisé pour la sélection des colonnes de la mémoire dynamique.

RAS est bien présent sur le BUS d’extension, nous l’appellerons TRS_ZMREQ.

CPLD ADRESSES

PIN = TRS_ZMREQ; /* DECLARATION DES SIGNAUX DE CONTROLE DU BUS */

PIN = TRS_RD;

PIN = TRS_WR;

Concernant l’adressage des données, qu’elles soient lues ou écrites, les adresses sont imposées par le processeur. On sait qu’elles sont stables lorsque TRS_ZMREQ est actif, et qu’elles sont présentes au moins une fois lors d’un cycle d’accès mémoire MCY6-7.

On souhaite que l’accès à la mémoire s’effectue dans une fenêtre d’adresse allant de ${$}$8000 à ${$}$FFFF, l’accès est donc valide uniquement si A15=1.

Nous allons recréer le signal de demande d’accès à la mémoire MREQ.

CPLD ADRESSES

NODE MREQ; /* DECLARATION DE MEMORISATION DE DEMANDE D’ACCES A LA MEMOIRE */

MREQ.d = TRS_A15 & !TRS_ZMREQ ; /* SI A15= ‘1’ et TRS_ZMREQ=RAS = ‘0’

MREQ.ck = !CLK ;

Déclarons maintenant les signaux utiles à gestion de l’accès à la mémoire :

CPLD ADRESSES

PIN = TRS_A15 ; /* BUS D’ADRESSE DU BUS D’EXTENSION */

PIN = TRS_A14 ;

PIN = TRS_A13 ;

PIN = TRS_A12 ;

PIN = TRS_A11 ;

PIN = TRS_A10 ;

PIN = TRS_A9 ;

PIN = TRS_A8 ;

PIN = TRS_A7 ;

PIN = TRS_A6 ;

PIN = TRS_A5 ;

PIN = TRS_A4 ;

PIN = TRS_A3 ;

PIN = TRS_A2 ;

PIN = TRS_A1 ;

PIN = TRS_A0 ;

PIN = MEM_A16 ; /* BUS D’ADRESSE DE LA MEMOIRE */

PIN = MEM_A15 ;

PIN = MEM_A14 ;

PIN = MEM_A13 ;

PIN = MEM_A12 ;

PIN = MEM_A11 ;

PIN = MEM_A10 ;

PIN = MEM_A9 ;

PIN = MEM_A8 ;

PIN = MEM_A7 ;

PIN = MEM_A6 ;

PIN = MEM_A5 ;

PIN = MEM_A4 ;

PIN = MEM_A3 ;

PIN = MEM_A2 ;

PIN = MEM_A1 ;

PIN = MEM_A0 ;

Afin de réaliser un transfert mémoire il faut positionner le bus d’adresse MEM_Ax en y recopiant les valeurs de TRS_Ax lorsqu’un transfert est initié soit les équations suivantes :

CPLD ADRESSES

MEM_A0.d = TRS_A0 & MREQ & MCY2 & MCY1 /* MEM_Ax = TRS_Ax SI MREQ VALIDE ET PENDANT LE CYCLE MCY6-7 */

…

MEM_Ax.d = TRS_Ax & MREQ & MCY2 & MCY1

MEM_A0.ck = CLK ; /* SYNCHRONISATION SUR CLK POUR QUE LES VALEURS MCYx SOIENT STABLES */

…

MEM_Ax.ck = CLK ;

A ce point nous n’avons pas encore fixé les registres permettant de gérer la pagination de la fenêtre de 16ko. Mais peu importe, il s’agit de valider l’accès à la mémoire. Nous pouvons cependant sélectionner l’une ou l’autre des mémoires, vidéo ou extension mémoire, car les fenêtres d’accès sont différentes :

- Extension mémoire de ${$}$8000 à ${$}$BFFF => A15= ‘1’, A14 = ‘0’.

- Mémoire vidéo de ${$}$C000 à ${$}$FFFF => A15= ‘1’, A14 = ‘1’.

CPLD ADRESSES

PIN = MEM_CS0 ; /* DECLARATION DES SIGNAUX DE SELECTION DES BOITIERS MEMOIRE */

PIN = MEM_CS1 ;

MEM_CS0 = A15 & !A14 ;

MEM_CS1 = A15 & A14 ;