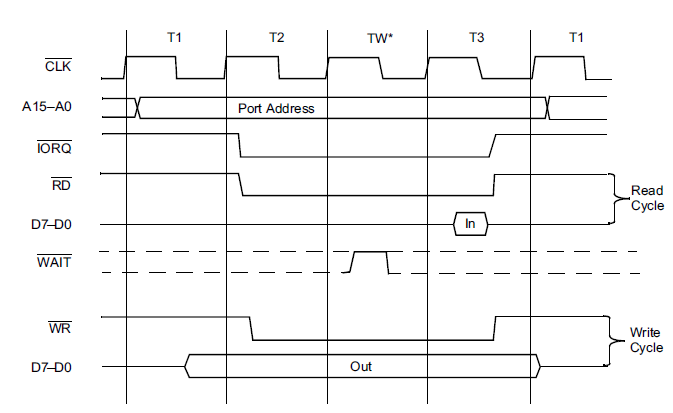

Chaque plan couleur est adressage grâce aux bit CTRL_PLC0 et CTRL_PLC1 du registre CTRL. Il nous faut donc tout d’abord créer ce registre et gérer les échanges de l’ordinateur au travers des ports périphériques. En voici le chronogramme.

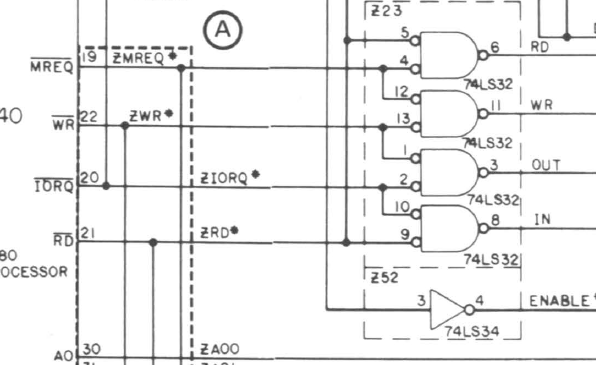

De la même manière que pour la mémoire on remarque que les signaux et indiquent le sens de l’échange et qui signale la validité de l’échange. Comme pour la mémoire le signal n’est pas disponible sur le bus d’extension.

On retrouve cependant des signaux IN et OUT produit à partir de WR, RD et IORQ . Ce sont ces signaux que nous allons utiliser en les renommant TRS_ZIN et TRS_ZOUT.

CPLD ADRESSES

PIN = INOUT ; /* SIGNALISATION D’UNE REQUETE D’ENTREE SORTIE */

PIN = TRS_ZIN ;

PIN = TRS_ZOUT ;

INOUT.d = (!TRS_ZIN # !TRS_ZOUT) ;

INOUT.ck = !CLK ;

L’avantage de la gestion des ports d’entrées et sorties, c’est que la donnée à destination du périphérique est également présente sur le bus d’adresse, ce qui permet de mémoriser la donnée simultanément sur les deux CPLD.

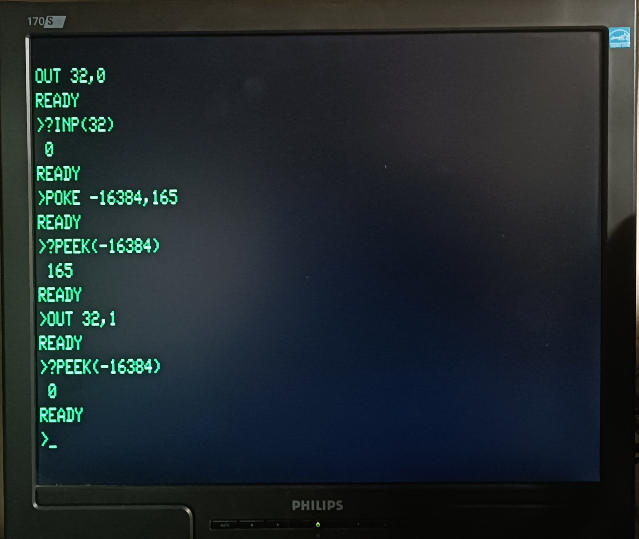

Il faut fixer les ports périphériques et je réserve donc arbitrairement les ports 32 à 35 ($20 à $23). Pour ces ports les poids forts sont nul sauf D5. L’adresse du port se trouve donc sur l’octet de poids faible (A0-A7) et la donnée sur les poids forts (A8-A15).

Si l’on ajoute au signal MREQ la transaction sur les ports périphériques, il devient :

CPLD ADRESSES

MREQ.d = A15 & !TSR_ZMREQ # !A7 & !A6 & A5 & !A4 & !A3 & (!TRS_ZIN # !TRS_ZOUT) ;/* TRANSACTION MEMOIRE OU PERIPHERIQUE */

MREQ.ck = !CLK ;

On peut alors mémoriser CTRL_PL1 et CTRL_PL0 issus d’une fonction OUT.

CPLD ADRESSES

NODE [CTRL_PL1..0] ;

CTRL_PL0.d = A8 ; /* MEMORISATION DE D0 DANS CTRL_PL0*/

CTRL_PL0.ck = MREQ & INOUT & !RDWR & !A0 & !A1 ; /* PORT $20 (001000[A1=0; A0=0]) */

CTRL_P1.d = A9 ; /* MEMORISATION DE D1 DANS CTRL_PL1*/

CTRL_P1.ck = MREQ & INOUT & !RDWR & !A0 & !A1 ;

Il doit être cependant possible de relire l’état de ce registre et cela se passe sur le CPLD Données pour lequel il faut indiquer quel registre est adressé (car le bus d’adresse n’est pas connu de ce CPLD) et l’information de traitement d’un port périphérique INOUT.

CPLD ADRESSES

PIN = CSREG0 ; /* SIGNAUX DE SELECTION DES REGISTRES */

PIN = CSREG1 ;

CSREG0 = MREQ & INOUT & A0 ; /* RECOPIE DES POIDS FAIBLES QUI DESIGNENT LES NUMEROS DE PORTS */

CSREG1 = MREQ & INOUT & A1 ;

Ce qui donne pour la mémorisation du registre, une lecture du bus donnée lorsque l’on a une transaction (MREQ) en écriture (!RDWR) sur le port périphérique (INOUT) $20[CSREGx].

CPLD DONNEES

PIN INOUT ;

PIN CSREG0 ;

PIN CSREG1 ;

NODE [CTRL_PL1..0] ;

CTRL_PL0.d = D0 ;

CTRL_PL1.d = D1 ;

CTRL_PL0.ck = MREQ & !RDWR & INOUT & CLK & !CSREG0 & !CSREG1 ;

CTRL_PL1.ck = MREQ & !RDWR & INOUT & CLK & !CSREG0 & !CSREG1 ;

Pour la relecture du registre il faut positionner le bus de données à la valeur du registre au moment où INOUT et la sélection de registre correspondent. Les Bits D0 et D1 viennent donc se cumuler avec la lecture de la mémoire.

CPLD DONNEES

TRS_D0.d = RDWR & (MD0 & !INOUT # REG0 & INOUT & !CSREG0 & !CSREG1) ;

TRS_D1.d = RDWR & (MD1 & !INOUT # REG1 & INOUT & !CSREG0 & !CSREG1) ;

Il est maintenant possible de rendre accessible les quatre plans vidéo en modifiant les lignes d’adresses MA14 et MA15 comme suit :

CPLD ADRESSES

MEM_A14.d = CTRL_PL0 & MREQ & MCY2 & MCY1 ;

MEM_A15.d = CTRL_PL1 & MREQ & MCY2 & MCY1 ;

Voici ce que l’on peut obtenir.

Il ne reste qu’un pas à franchir pour la sélection des pages grâce à PGL :

CPLD ADRESSES

MEM_A16 = CTRL_PGE & MREQ & MCY2 & MCY1 ;

Et si on fait le parallèle pour la mémoire de l’extension, qui se différencie par la valeur de A14 on obtient finalement.

CPLD ADRESSES

MEM_A14.d = MREQ & (TRS_A14 & CTRL_PL0 # !TRS_A14 & CTLA_M0) & MCY2 & MCY1 ;

MEM_A15.d = MREQ & (TRS_A14 & CTRL_PL1 # !TRS_A14 & CTLA_M1) & MCY2 & MCY1 ;

MEM_A16.d = MREQ & (TRS_A14 & PGE # !TRS_A14 & CTLA_M2) & MCY2 & MCY1 ;